Field-Effect Transistors - General Questions (2)

- Home

- Electronics & Communication Engineering

- Electronic Devices and Circuit Theory

- Field-Effect Transistors - General Questions

Field-Effect Transistors - General Questions

| 9. |

|

|||||||

Answer: Option D Explanation: No answer description available for this question |

| 10. |

|

|||||||

Answer: Option B Explanation: No answer description available for this question |

| 11. |

|

|||

Answer: Option A Explanation: No answer description available for this question |

| 12. |

|

|||||

Answer: Option A Explanation: No answer description available for this question |

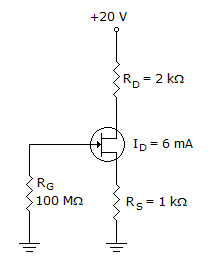

| 13. | Refer to figure show below. Calculate the value of VD.

|

|||||||

Answer: Option C Explanation: No answer description available for this question |

| 14. |

|

|||||||

Answer: Option D Explanation: No answer description available for this question. |

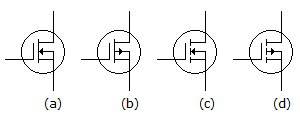

| 15. | Identify the n-channel D-MOSFET.

|

|||||||

Answer: Option A Explanation: o answer description available for this question |

| 16. |

|

|||

Answer: Option A Explanation: No answer description available for this question |